## 40W High-Integration, High-Efficiency PMIC for Wireless Power Transmitter

### BA?P NAO

- VIN Input Voltage Range: 4.2V-30V

- PVIN Input Voltage Range: 1V~26V

- Up to 40W Power Transfer

- Integrated Full-Bridgefer

## NAREOEK DEOPKNU

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Revision 1.0: Production

Revision 1.1: Update DEVICE ORDER INFORMATION and Description

### ARE AKN ANE BKNI 2PEK

| ORDERABLE<br>DEVICE | PACKAGING<br>TYPE | STANDARD<br>PACK QTY | PACKAGE<br>MARKING | PINS | PACKAGE DESCRIPTION |

|---------------------|-------------------|----------------------|--------------------|------|---------------------|

| SCT63340FGAR        | Tape & Reel       | 5000                 | 3340               | 21   | QFN-21L             |

## **OKH PAI 2TEL I N2PE CO**

Over operating free-air temperature unless otherwise noted<sup>(1)</sup>

| DESCRIPTION                                               | MIN  | MAX | UNIT |

|-----------------------------------------------------------|------|-----|------|

| VIN                                                       | -0.3 | 32  | V    |

| PVIN1, PVIN2                                              | -0.3 | 28  | V    |

| SW1,SW2                                                   | -1   | 28  | V    |

| SW3                                                       | -1   | 32  | V    |

| BST1,BST2                                                 | -0.3 | 34  | V    |

| BST3                                                      | -1   | 38  | V    |

| BST1-SW1,BST2-SW2,BST3-SW3                                | -0.3 | 6   | V    |

| VDD, V3P3, VDM, EN, PWM1,<br>PWM2, ISNS, IDMO, VDMO, QDET | -0.3 | 6   | V    |

| Operating junction temperature TJ <sup>(2)</sup>          | -40  | 125 | °C   |

| Storage temperature TSTG                                  | -65  | 150 | °C   |

### LE K BEC N<sup>2</sup> PEK

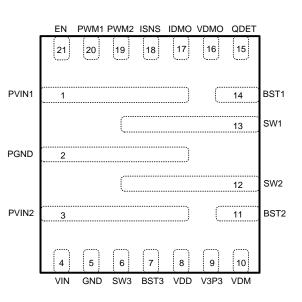

Figure 1. Top view 21-Lead QFN 4mm\*4mm

(1) Stresses beyond those listed under Absolute Maximum Rating may cause device permanent damage. The device is not guaranteed to function outside of its Recommended Operation Conditions.

(2) The IC includes over temperature protection to protect the device during overload conditions. Junction temperature will exceed 150°C when over temperature protection is active. Continuous operation above the specified maximum operating junction temperature will reduce lifetime.

### LE B PEK O

| NAME  | NO. | PIN FUNCTION                                                                                                                                                                                                                                                       |

|-------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PVIN1 | 1   | Input supply voltage of half-bridge FETs Q1 and Q2. Connected to the drain of high side FET Q1. a local bypass capacitor from PVIN1 pin to PGND pin should be added. Path from PVIN1 pin to high frequency bypass capacitor and PGND must be as short as possible. |

| PGND  | 2   | PGND is the common power ground of the full bridge, connected to the source terminal of low side FETs Q2 and Q4 internally.                                                                                                                                        |

| PVIN2 | 3   | Input supply voltage of half-bridge FETs Q3 and Q4. Connected to the drain of high side FET Q3. Local bypass capacitor from PVIN1 pin to PGND pin should be added. Path from PVIN1 pin to high frequency bypass capacitor and PGND must be as short as possible.   |

2For more information www.silicontent.com, Product Folder Links: SCT63340

| VIN  | 4  | Input supply voltage of the Buck converter. Add a local bypass capacitor from VIN pin to GND pin. Path from VIN pin to high frequency bypass capacitor and GND must be as short as possible. |

|------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND  | 5  | Power ground of the Buck converter.                                                                                                                                                          |

| SW3  | 6  | Switching output of the Buck converter. Connect SW3 to an external power inductor.                                                                                                           |

| BST3 | 7  | Power supply bias for the high-side power MOSFET gate driver of Buck converter.<br>Connect a 0.1uF capacitor from BST3 pin to SW3 pin.                                                       |

| VDD  | 8  | Output voltage of the Buck converter. Connect 22uF capacitor from this pin to GND pin. VDD is also the input power supply for gate driver of power stage and the 3.3V LDO.                   |

| V3P3 | 9  | 3.3V LDO output. Connect 1uF capacitor to ground.                                                                                                                                            |

| VDM  | 10 | High-                                                                                                                                                                                        |

## PDANI 2HE BKNI 2PEK

| PARAMETER | THERMAL METRIC                                        | QFN-21L | UNIT   |

|-----------|-------------------------------------------------------|---------|--------|

| R         | Junction to ambient thermal resistance <sup>(1)</sup> | 40      | °C /// |

| R         | Junction to case thermal resistance <sup>(1)</sup>    | 24      | °C/W   |

(1) SCT provides R and R numbers only as reference to estimate junction temperatures of the devices. R and R are not a characteristic of package itself, but of many other system level characteristics such as the design and layout of the printed circuit board (PCB) on which the SCT63340 is mounted, thermal pad size, and external environmental factors. The PCB board is a heat sink that is soldered to the leads of the SCT63340. Changing the design or configuration of the PCB board changes the efficiency of the heat sink and therefore the actual R and R.

# SCT63340

| SYMBOL           | PARAMETER                            | TEST CONDITION                               | MIN   | ΤΥΡ | MAX   | UNIT |

|------------------|--------------------------------------|----------------------------------------------|-------|-----|-------|------|

| RDSON_L          | Low side FET on-resistance           |                                              |       | 250 |       |      |

| Tss              | Internal soft-start time             |                                              |       | 1.4 |       | ms   |

| 3.3V LDO         |                                      |                                              |       |     |       |      |

| V <sub>3P3</sub> | Output voltage                       | Cout=1uF, VDD=5V                             | 3.267 | 3.3 | 3.333 | V    |

| I <sub>3P3</sub> | Output current Capability            |                                              |       | 220 |       | mA   |

| I <sub>SC1</sub> | Short current                        |                                              |       | 40  |       | mA   |

| Current Se       | nse                                  |                                              |       |     |       |      |

| VISNS0           | Voltage with no input current        | I <sub>PGND</sub> =0A ,Tj=25<br>PWM1=PWM2=0V | 0.585 | 0.6 | 0.615 | V    |

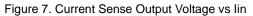

| RISNS            | Input current to output voltage gain | VISNS=VISNS0+IPGND*RISNS                     | 0.98  |     |       |      |

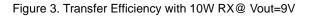

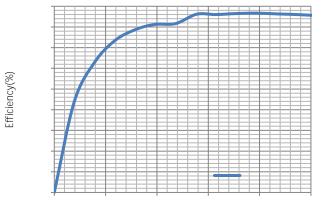

## PULE 2 H D2 N2 PANKOPE O

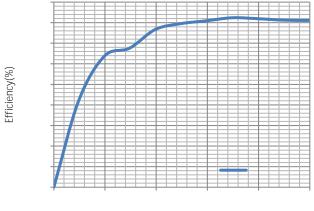

Output Power(W)

Figure 2. Transfer Efficiency with 5W RX@ Vout=5V

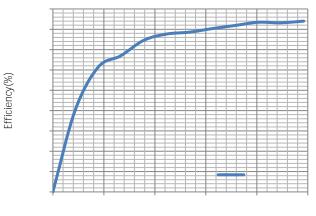

Output Power(W)

Output Power(W)

**三二二** 苗 洲科技

Efficiency(%)

Iload(A)

For more information <u>www.silicontent.com</u>, Product Folder Links: SCT63340 © 2019 Silicon Content Technology Co., Ltd. All Rights Reserved7

8For more information <u>www.silicontent.com</u>, Product Folder Links: SCT63340

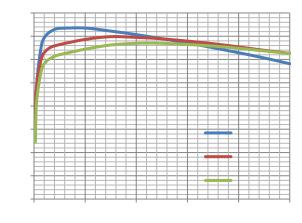

#### 5V Output Buck Converter

The SCT63340fully integrates synchronous buck converter with up to 30V input voltage and 5V fixed output voltage, which offers up to 1A output current capability. The device employs 450KHz fixed fredEarOry Ms2k/Spare/67.34ng1472 mode control with the internal loop compensation network and built-in 1.4ms soft-start which makes this buck converter easily to be used by minimizing the off-chip compot/(ent-b3) at BDB 7555(pp)M50M5001200Th(PSM) 03G g45()] TJ adopted to increase the light load efficiency.

The buck converter's output, a fixed 5V voltage, **gg560**rts the power requirement on system such as transmitter controller or mechanical fan meanwhile it is also the power supply of the SCT63340's 3.3V LDO and gate drivers of 4-MO6()MCID 79/Lang (e0009m37(oE009(n)4)5(s)-5(o/Span &MCID 80/Lang (en-US) BDC q0.00000912 0 612 792 reW\* n

#### Full Bridge Over Current Protection

The SCT63340 integrates cycle-by-cycle current limit and hiccup mode for over-current protection. The current of the high side FET Q1and Q3 is sensed and compared to the current limit threshold during each switching cycle. If the current exceeds the threshold, 12.5A typical, the high side FET turns off immediately in present cycle to avoid current increasing further even that PWM signal still stays in high level. The over current counter is incremented. If one high side FET occurs over current in 5 consecutive cycles, then all 4 internal FETs are turned off regardless of the PWM inputs. The full bridge enters hiccup mode and will attempt to restart after a time-out period of 24ms typically.

### **Current Sense**

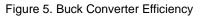

The SCT63340 has a proprietary lossless average current sensing circuit that measures the average input current of full bridge with  $\pm 2\%$  accuracy and reports a proportional voltage directly to the ISNS pin. This voltage information on ISNS pin can be sent to application specific controller ASIC or general MCU for Foreign Object Detection FOD and current demodulation.

When the full bridge of MOSFETs does not work, no current flows to PGND. The DC bias voltage on ISNS pin is 600mV. This DC bias helps set up a suitable voltage bias for the following analog to digital converter in MCU or amplifier for current demodulation. The average input current to voltage conversion gain on ISNS is 1V/A. The equation 3 represent the corresponding relation for the output voltage on ISNS pin and average current to PGND from full bridge.

$$V_{\rm ISNS} = 600 \,\mathrm{mV} + I_{\rm PGND} * 1 \,\mathrm{V/A} \tag{3}$$

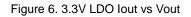

### 3.3V LDO

The SCT63340 has an integrated low-dropout voltage regulator which powered from VDD and supply regulated 3.3V voltage on V3V pin. The output current capability is 200mA. This LDO can be used to bias the supply voltage of MCU directly.

It is recommended to connect a decoupling ceramic capacitor of 1uF to 10uF to the V3V pin. Capacitor values outside of the range may cause instability of the internal linear regulator.

### **Q** Factor Detection

The SCT63340 integrated a low cost, reliable Q factor detection circuit to assure foreign objects detection before the selection phase. It generates a small pulse to detect any foreign object on the transmitter coil, it can detect metal on the transmitter coil easily.

After chip enable, apply a low voltage level pulse to EN pin can trigger the Q factor detection feature. The pulse width should be longer than 50us but less than 200us. SW1 will be preset to 2V for 4.7ms and then pull low to ground and this apply power to LC resonant loop and Vcoil will appear damping oscillation after SW1 short to ground. The SCT63340 will generate a pulse on VDMO pin and MCU can capture this pulse to calculate the Q factor by the pulse width as the Equation 4 shows. PWM1 and PWM2 should be low in Q factor detection phase.

$$Q = \frac{\Delta T * \pi}{10 * \ln \frac{V_{TH} - HIGH}{V_{TH} LOW}}$$

(4)

where

- $\Delta T$  is the pulse width on VDMOS pin

- VTH\_HIGH is high threshold 0.2V

- VTH\_LOW is low threshold 0.1V

### **Voltage and Current Demodulation**

The SCT63340 integrates two demodulation schemes, one based on coil voltage information calling voltage demodulation and the other based on input average current information calling current demodulation.

### **2 LLHE 2PEK E BKNI 2PEK**

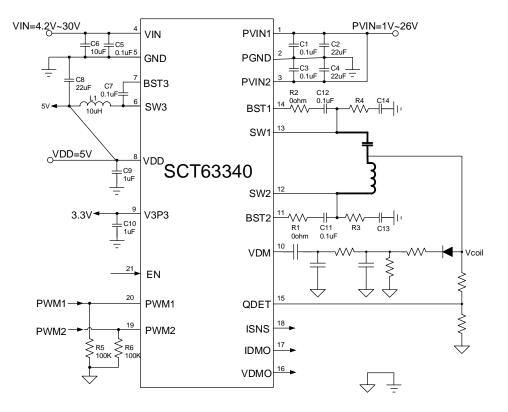

### **Typical Application**

Figure 11. Separate Input to VIN and PVIN

**Application Waveforms**

Figure 12. Power Up

Figure 13. Power Down

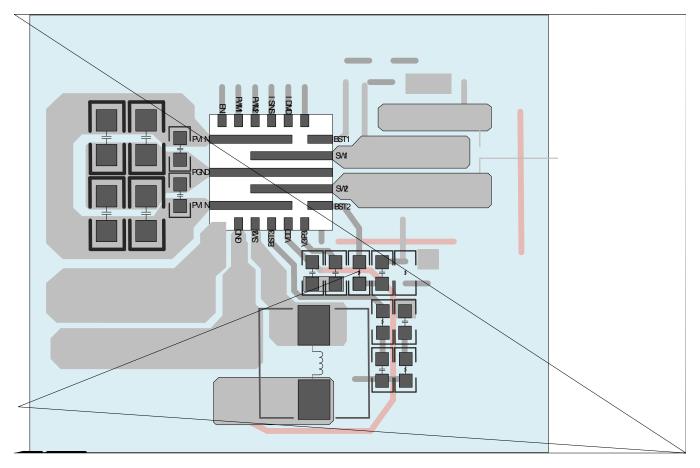

### Layout Guideline

Proper PCB layout is a critical for SCT63340

currents or voltages are easy to interact with stray inductance and parasitic capacitance to generate noise and degrade performance. For better results, follow these guidelines as below:

- 1. Bypass capacitors from PVIN to PGND should put next to PVIN and PGND pin as close as possible especially for the two small capacitors.

- 2. PGND connect to bottom layer by via between capacitors.

- 3. Bypass capacitors from VIN to GND should put next to VIN and GND pin as close as possible especially for the small capacitor.

- 4. Buck converter output capacitor's ground should connect to GND directly to minimize the power loop.

- 5. VDD pin can connect to the DC/DC's output capacitor from bottom layer, connect to the point behind the capacitor while not connect to inductor.

- 6. Bypass capacitor for VDD place next to VDD pin.

- 7. Bypass capacitor for V3P3 place next to V3P3 pin.

Figure 18. PCB Layout Example

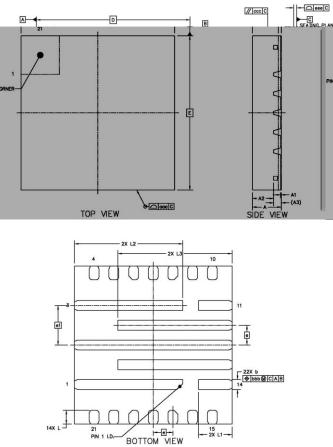

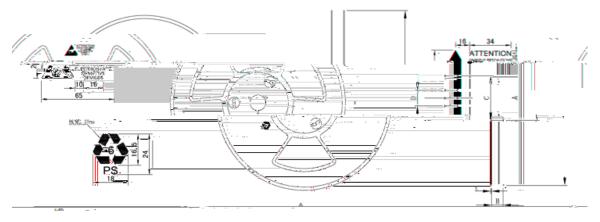

### L? G?CAE BKNI ?PEK

|                      |             | SYMBOL | MIN   | NOM     | MAX  |  |

|----------------------|-------------|--------|-------|---------|------|--|

| TOTAL THICKNESS      | A           | 0.7    | 0.75  | 0.8     |      |  |

| STAND OFF            |             | A1     | 0     | 0.02    | 0.05 |  |

|                      |             |        |       |         |      |  |

| I A S III            |             | b      | 0.2   | 0.25    | 0.   |  |

| DODY DITE            | BODY SIZE X |        | 4 BSC |         |      |  |

| BODY SIZE            |             |        |       | :       |      |  |

| LEAD PITCH           |             | e      |       | 0.5 BSC |      |  |

| LEAD PITCH           |             | e1     | 1 BSC |         |      |  |

|                      |             | L      | 0.25  | 0.35    | 0.4  |  |

|                      |             | L1     | 0.75  | 0.85    | 0.9  |  |

| LEAD LENGTH          | LEAD LENGTH |        | 2.65  | 2.75    | 2.8  |  |

|                      |             | L3     | 2.8   | 2.9     | 3    |  |

| DACKACE EDGE TO EDAN | 0E          |        |       |         |      |  |

#### NOTE:

- 1. Drawing proposed to be made a JEDEC package outline MO-220 variation.

- 2. Drawing not to scale.

- 3. All linear dimensions are in millimeters.

- 4. Thermal pad shall be soldered on the board.

- 5. Dimensions of exposed pad on bottom of package do not include mold flash.

- 6. Contact PCB board fabrication for minimum solder mask web tolerances between the pins.

16For more information <u>www.silicontent.com</u>, Product Folder Links: SCT63340

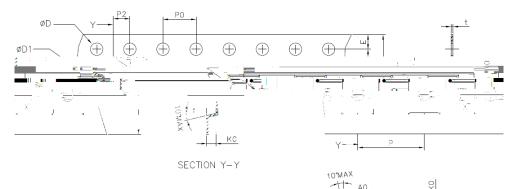

# P2 LA2 NAAHE BKNI 2PEK

SCALE: 1 : 1

SECTION A-A

**REEL DIMENSIONS**

| Reel Width | A      | В      | С      | D         | t       |

|------------|--------|--------|--------|-----------|---------|

| 12         | Ø329±1 | 12.8±1 | Ø100±1 | Ø13.3±0.3 | 2.0±0.3 |

SECTION X-X

TAPE DIMENSIONS

| W              | A0        | B0        | K0        | t         | P      |

|----------------|-----------|-----------|-----------|-----------|--------|

| (mm)           | (mm)      | (mm)      | (mm)      | (mm)      | (mm)   |

| +0.30<br>-0.10 | 3.40±0.10 | 4.40±0.10 | 1.14±0.10 | 0.25±0.02 | 8±0.10 |

| E         | F         | P2        | D          | D1         | P0        | 10P0      |

|-----------|-----------|-----------|------------|------------|-----------|-----------|

| (mm)      | (mm)      | (mm)      | (mm)       | (mm)       | (mm)      | (mm)      |

| 1.75±0.10 | 5.50±0.05 | 2.00±0.05 | +0.10<br>0 | +0.25<br>0 | 4.00±0.10 | 40.0±0.20 |

For more information <u>www.silicontent.com</u>, Product Folder Links: SCT63340

$\ensuremath{\textcircled{C}}$  2019 Silicon Content Technology Co., Ltd. All Rights Reserved17

# NAH2PA L2NPO

| PN       | DESCRIPTION                                                                          | COMMENTS |

|----------|--------------------------------------------------------------------------------------|----------|

| SCT63240 | Up to 20W High Integration High<br>Efficiency PMIC for Wireless<br>Power Transmitter |          |